# LS7267 Registers:

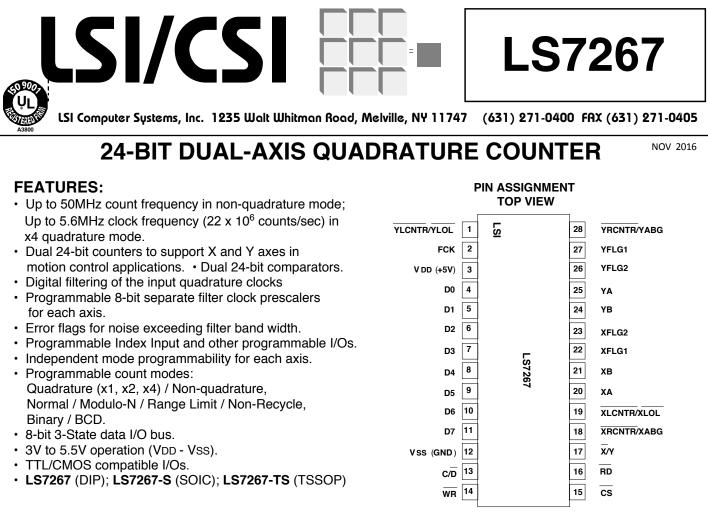

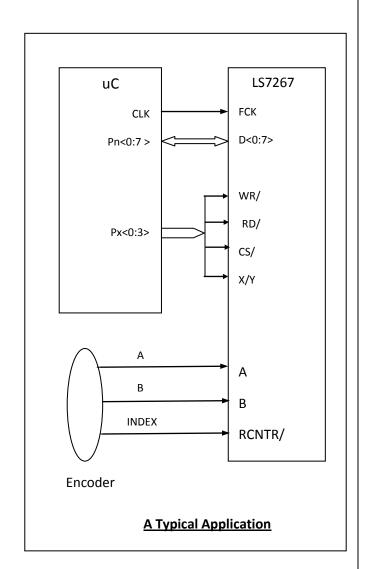

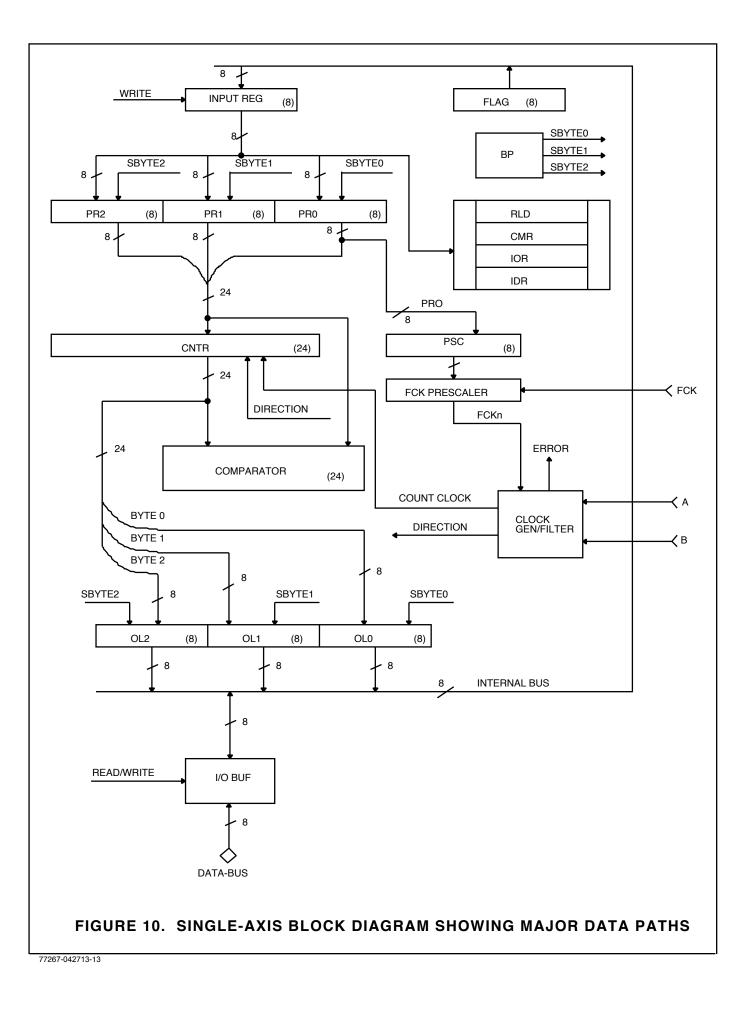

LS7267 has a set of registers associated with each X and Y axis. All X-axis registers have the name prefix X, whereas all Y-axis registers have the prefix Y. Selection of a specific register for Read/Write is made from the decode of the three most significant bits (D7 - D5) of the data-bus. CS input enables the IC for Read/Write. C/D input selects between control and data information for Read/Write. Following is a complete list of LS7267 registers.

#### Preset Registers: XPR and YPR

Each of these PRs are 24-bit wide. 24-bit data can be written into a PR, one byte at a time, in a sequence of three data write cycles.

Γ

# Counters: XCNTR and YCNTR

Each of these CNTRs are 24-bit synchronous Up/Down counters. The count clocks for each CNTR is derived from its associated A/B inputs. Each CNTR can be loaded with the content of its associated PR.

### **Output Latches: XOL and YOL**

Each OL is 24-bits wide. In effect, the OLs are the output ports for the CNTRs. Data from each CNTR can be loaded into its associated OL and then read back on the data-bus, one byte at a time, in a sequence of three data Read cycles.

### Byte Pointers: XBP and YBP

The Read and Write operations on an OL or a PR always accesses one byte at a time. The byte that is accessed is addressed by one of the BPs. At the end of every data Read or Write cycle on an OL or a PR, the associated BP is automatically incremented to address the next byte.

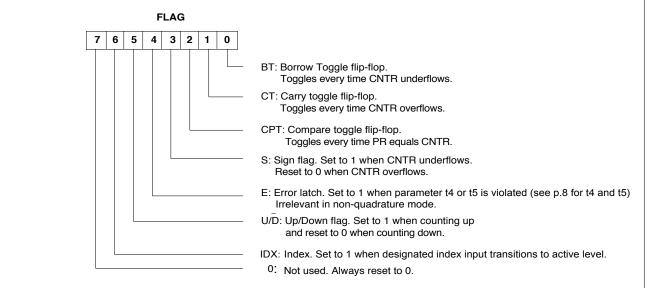

# Flag Register: XFLAG and YFLAG

The FLAG registers hold the status information of the CNTRs and can be read on the data bus. All bits excepting the E and the IDX bits change dynamically to represent the instantaneous status of the CNTR's. In contrast the E and the IDX bits are latched. Once set they can only be reset via the RLD registers.

#### Filter Clock Prescalers: XPSC and YPSC

Each PSC is an 8-bit programmable modulo-n down counter, driven by the FCK input. The division factor n is stored into each PSC from its associated PR register low byte, PR0. The PSCs provide the ability to generate independent filter clock frequencies for each channel used for filtering the quadrature clocks applied at the A and B inputs in quadrature mode. The same filter clocks are also used for filtering the designated INDEX inputs.

The effective internal filter clock frequency is:  $f_{FCKn} = (f_{FCK}/(n+1))$ , where n = PSC = 0 to h'FF and  $f_{FCK}$  is the clock frequency at the FCK input. For proper operation the required condition is:  $f_{FCKn} > 8f_{QA}$  (or  $8f_{QB}$ ), where  $f_{QA}$  (or  $f_{QB}$ ) is the frequency at A (or B) input. The FCK pin is not used in non-quadrature mode and should be tied off to VDD.

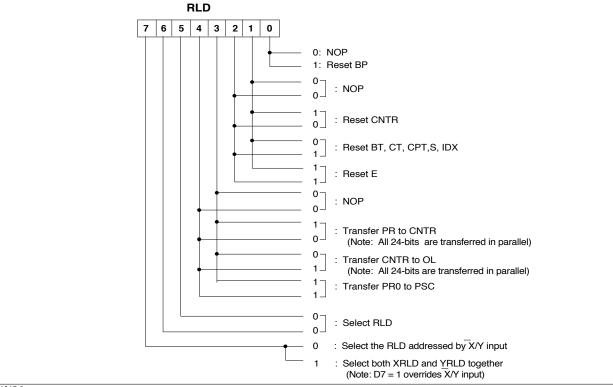

#### Reset and Load Signal Decoders: XRLD and YRLD

Following functions can be performed by writing a control byte into an RLD: Transfer PR to CNTR, Transfer CNTR to OL, reset CNTR, reset FLAG and reset BP.

# Counter Mode Registers: XCMR and YCMR

The CNTR operational mode is programmed by writing into the CMRs.

### **DEFINITIONS OF COUNT MODES:**

**Range Limit**. In range limit count mode, an upper and a lower limit is set, mimicking limit switches in the mechanical counterpart. The upper limit is set by the content of the PR and the lower limit is set to be 0. The CNTR freezes at CNTR = PR when counting up and at CNTR = 0 when counting down. At either of these limits, the counting is resumed only when the count direction is reversed.

**Non-Recycle**. In non-recycle count mode, the CNTR is disabled, whenever a count overflow or underflow takes place. The end of cycle is marked by the generation of a Carry (in Up Count) or a Borrow (in Down Count). The CNTR is re-enabled when a reset or load operation is performed on the CNTR.

**Modulo-N.** In modulo-N count mode, a count boundary is set between 0 and the content of PR. When counting up, at CNTR = PR, the CNTR is reset to 0 and the up count is continued from that point. When counting down, at CNTR = 0, the CNTR is loaded with the content of PR and down count is continued from that point.

The modulo-N is true bidirectional in that the divide-by-N output frequency is generated in both up and down direction of counting for same N and does not require the complement of N in the UP instance. In frequency divider application, the modulo-N output frequency can be obtained at either the Compare (FLG1) or the Borrow (FLG2) output. Modulo-N output frequency,  $f_N = (f_i / (N+1))$  where  $f_i =$  Input count frequency and N = PR.

> The information included herein is believed to be accurate and reliable. However, LSI Computer Systems, Inc. assumes no responsibilities for inaccuracies, nor for any infringements of patent rights of others which may result from its use.

|                                                         | IOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 6 5                                                   | 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                         | 0 : Disable inputs A and B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                         | 1 : Enable inputs A and B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                         | 0 : <u>LCNTR/LOL</u> pin is Load CNTR input     1 : LCNTR/LOL pin is Load OL input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                         | 0 : RCNTR/ABG pin is Reset CNTR input     1 : RCNTR/ABG pin is A and B Enable gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                         | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$ : FLG1 pin is CARRY output; FLG2 pin is BORROW output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                         | 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 - 0 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                         | FLG1 is INDX (low pulse at INDEX pin active level); FLG2 is E (FLAG register bit 4)     (For FLG1 to output INDX, IDR bit0 must be set to 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         | 0 : Select IOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| └ <b>┭</b>                                              | 0: Select IOR addressed by X/Y input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                         | 1: Select both XIOR and YIOR together (Note: D7=1 overrides X/Y input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Either the                                              | CONTROL REGISTERS: XIDR and YIDR<br>e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously conde is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously conde is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously conde is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously of mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b> 7 6 5 4 3 2 0   0: Disable Index mode 1: Enable Index mode   1: Enable Index mode 0: Negative Index Polarity   1: Positive Index Polarity 1: Positive Index Polarity                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously of mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,<br>NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign<br>nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i<br>EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously<br>mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b><br><b>7 6 5 4 3 2 1 0</b><br><b>0</b> : Disable Index mode<br>1: Enable Index mode<br>0: Negative Index Polarity<br>1: Positive Index Polarity<br>0: <u>LCNTR/LOL</u> pin in index mode (See Note 1)<br>1: RCNTR/ABG pin in index mode (See Note 2)<br>Not used                                                                                                                                                                                                                                                                                                                                     |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,<br>NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign<br>nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i<br>EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously<br>c mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b><br><b>************************************</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,<br>NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign<br>nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i<br>EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously<br>mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b><br><b>7 6 5 4 3 2 1 0</b><br><b>0</b> : Disable Index mode<br>1: Enable Index mode<br>1: Enable Index mode<br>0: Negative Index Polarity<br>1: Positive Index Polarity<br>0: LCNTR/LOL pin in index mode (See Note 1)<br>1: RCNTR/ABG pin in index mode (See Note 2)<br>Not used<br><b>1</b> _: Select IDR<br><b>0</b> : Select IDR addressed by X/Y input                                                                                                                                                                                                                                          |

| Either the<br>NDEX n<br>Load_CN<br>being ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR, NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously of mode is unconditionally disabled in non-quadrature mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Either the<br>NDEX n<br>_oad_CN<br>peing ge<br>non-IND  | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,<br>NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign<br>nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i<br>EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously<br>at mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b><br><b>7 6 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 6 7 7 7 6 7 7 7 6 7 7 7 6 7 7 7 6 7 7 7 6 7 7 7 6 7 7 7 7 6 7 7 7 7 6 7 7 7 7 7 7 7 7 7 7</b>                                                                                                                                                                                                                                                                                                                                                                |

| Either the<br>INDEX n<br>Load_CN<br>being ge<br>non-IND | e LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate in the INDEX mode. In the<br>node the index signal from an encoder, applied to one of the two inputs performs either reset_CNTR,<br>NTR or Load_OL operation <b>synchronously</b> with the quadrature clocks, the internal load or reset sign<br>nerated at the same angular orientation of the encoder in both CW and CCW directions. In contrast i<br>EX mode these signals are applied <b>asynchronously</b> with respect to A/B inputs and act instantaneously<br>mode is unconditionally disabled in non-quadrature mode.<br><b>IDR</b><br><b>7 6 5 4 3 2 1 0</b><br><b>0</b> : Disable Index mode<br>1: Enable Index mode<br>1: Enable Index mode<br>0: Negative Index Polarity<br>1: Positive Index Polarity<br>1: RCNTR/LOL pin in index mode (See Note 1)<br>1: RCNTR/LOL pin in index mode (See Note 2)<br>Not used<br><b>1</b> J.: Select IDR<br><b>0</b> : Select IDR addressed by X/Y input<br>1: Select DR addressed by X/Y input<br>1: Select DR addressed by X/Y input<br>1: Select both XIDR and YIDR (Note: D7=1 overrides X/Y input)<br>Note 1: Function selected for this pin via IOR, becomes the operating INDEX function. |

# I/O pins:

Following is a description of all the input/output pins.

**YLCNTR/YLOL**/ (pin 1). Input. Programmable input in the y-axis which can be configured with the YIOR register to function as either LD\_YCNTR or LD\_YOL input. LD\_YCNTR causes the YPR to be loaded into YCNTR when the input is at active level. LD\_YOL causes YCNTR to be loaded into YOL when the input is at active level.

In quadrature mode the input can further be initialized with the YIDR register to function in either INDEX mode or non-INDEX mode. The INDEX mode allows for the direct interface with the INDEX output of an incremental encoder. In this mode the YLCNTR/YLOL/ input is sampled with the filter clock derived from the FCK input clock which is used for validating the quadrature clocks as well

In the INDEX mode the YCLNTR/YLOL/ input can be configured for either high or low active logic levels with the YIDR. In the non-INDEX mode the active level is not programmable and is unconditionally set to low active.

In the non-INDEX mode YCLNTR/YLOL/ input is not sampled with the filter clock and can be applied asynchronously with respect to YA and YB inputs. In non-quadrature mode the YCLNTR/YLOL/ input is unconditionally set to the non-INDEX mode.

**FCK**. (pin 2). Input. A clock applied at the FCK input is used for generating filter clocks for both X and Y axes. The filter clocks are used for validating the quadrature clocks (at XA, XB, YA and YB inputs), and the INDEX signal ( at XLCNTR/XLOL/ or XRCNTR/ or YLCNTR/YLOL/ or YRCNTR in INDEX mode). The clock at the FCK input is divided down separately by XPSC and YPSC prescalers to generate the filter clock for each axis. The prescaler output frequency is given by:  $f_{FCKn} = f_{FCK}/(n+1)$ , where  $f_{FCK}$  is the frequency at the FCK input and n = [XPSC] or [YPSC].

For proper operation in the quadrature mode the following condition of frequencies must be satisfied:  $f_{FCKn} \ge 8f_{QAB}$ , where  $f_{QAB}$  is the clock frequency at XA or XB or YA or YB input.

In non-quadrature mode the filter clock is not used and the FCK input must be tied off to either VDD or VSS.

**VDD** (pin 3). Supply voltage positive rail. +3V to +5V.

**D0** through **D7** (pins 4 through 11). Inputs/Outputs. The 8-bit databus D0 through D7 is a 3-state portal for the READ/WRITE operation in and of the device. The databus is common to both axes. During a read operation when both CS/ and RD/ inputs are low, the content of either the OL or the FLAG register of the selected axis is placed on databus. During a write operation the content of the databus is written into the selected register at the trailing edge of the WR/ pulse.

When CS/ is high the databus is disabled and placed in the high impedance state.

VSS (pin 12). Supply voltage negative rail or GND.

**D/C** (pin 13). Input. This input selects between a control register or a data register for read/write operation according to Table 1. When low, a write operation causes the content of the databus to be written into the selected PR register. When high, a write causes the databus to be written into the selected control register. During a read operation, a low at the D/C input causes the content of the selected OL to be output on the databus while a high causes the content of the selected FLAG register to be output on the databus.

**WR**/ (pin 14). Input. A low pulse at the WR/ input causes the content of the databus to be written into the selected register according to Table 1. The write operation is completed at the trailing edge of the WR/ pulse.

**CS**/ (pin 15). Input. A low at the CS/ input enables the device for read or write operations. When the CS/ input is high the read and write operations are disabled and the databus, D0-D7 is placed in the high impedance state.

**RD**/ (pin 16). Input. A low at the RD/ input causes the content of the selected register to be output on the databus according to Table 1.

**X/Y** (pin 17). Input. Selects between X and Y axis for read and write. A low at this input selects the X axis while a high selects the Y axis.

**XRCNTR/XABG** (pin 18). Input. Programmable input in the x-axis which can be configured with the XIOR register to function as either R\_XCNTR or E\_XAB input. R\_XCNTR causes the XCNTR to be reset to 0 when the input is in the active level. E\_XAB causes the input to function as the XA and XB enable/disable gate. In this mode XA and XB become enabled when the XRCNTR/XABG input is high and disabled when the input is low,

In quadrature mode the input can further be initialized with the XIDR register to function in either INDEX mode or non-INDEX mode. In the INDEX mode the XRCNTR/XABG is sampled with the filter clock derived from the FCK input clock which is used for validating the quadrature clocks as well.

When configured in the INDEX mode the XRCNTR/XABG input must also be configured as R\_XCNTR to function correctly. In the INDEX mode the XRCNTR/XABG input can be configured for either high or low active logic levels for the R\_XCNTR function via the XIDR register. In the non-INDEX mode the active level is not programmable and is unconditionally set to low active for the R\_XCNTR function.

In the non-INDEX mode XRCNTR/XABG input is not sampled with the filter clock and can be applied

asynchronously with respect to XA and XB inputs. In non-quadrature mode the XCNTR/XABG input is unconditionally set to the asynchronous mode

**XLCNTR/XLOL**/ (pin 19). Input. This is the x-axis functional equivalent of the YCLNTR/YLOL input. The associated x-axis reference registers are: XCNTR, XOL, XIOR and XIDR

**XA** (pin 20), **XB** (pin 21). Inputs. These are the A and B count inputs in the x-axis. These inputs can be configured to function either in quadrature mode or in non-quadrature mode. The configuration is made with the XCMR register. In quadrature mode, XA and XB clocks are normally supplied from incremental encoders with the two clocks being 90° out of phase. When XA leads XB in phase, the counter (XCNTR) counts up; when XA lags XB, the XCNTR counts down.

In non-quadrature mode XA functions as the count input and XB as the count direction control input. When XB is high positive transitions at the XA input causes the XCNTR to count up. Conversely, when XB is low positive transitions at the XA input causes the XCNTR to count down.

In quadrature mode XA and XB inputs are sampled for logic level validation and noise discrimination with an internal filter clock derived from the FCK input clock. In non-quadrature mode XA and XB inputs are not sampled and the count clocks are applied directly to the XCNTR count input bypassing the filter circuit.

**XFLG1** (pin 22). Output. Programmable output in the xaxis to function as CARRY or BORROW or COMPARE or INDX. The configuration is made with the XIOR register. The output is generated as a low pulse when the selected event takes place CARRY or BORROW output is generated when the XCNTR overflows or underflows respectively. INDX output is generated when the designated INDEX input goes into active level. COMPARE output is generated at XCNTR = XPR. An exception is made in the **modulo-N** and **range-limit** modes In these modes the COMPARE output is generated at XCNTR = XPR only in the **up** count direction.

**XFLG2** (pin 23). Output. Programmable output in the x-axis to function as BORROW or UP/DN or E. The configuration is made with the XIOR register. The BORROW output is generated as a low pulse when the XCNTR underflows. When configured as UP/DN the output dynamically goes high when the XCNTR is counting up and low when it is counting down. When configured as E, XFLG2 switches low whenever the following condition exists:  $t_4 \le t_3$  or  $t_5 \le 2t_3$  (see page 8). It remains low until the FLAG register bit-4 is reset whereupon XFLG2 output switches high.

**YA** (pin25), **YB** (pin 24). Inputs. These are the y-axis functional equivalents of the XA and XB inputs. They operate on the YCNTR and are configured with the YCMR register.

**YFLG2** (pin26), Output. This is the y-axis functional equivalent of XFLG2 .

**YFLG1** (pin27), Output. This is the y-axis functional equivalent of XFLG1

**YRCNTR/YABG** (pin 28). Input. This is the y-axis functional equivalent of the XRCNTR/XABG input. The associated y-axis reference registers are: YCNTR, YOL, YIOR and YIDR .

| REGISTER ADDRESSING MODES (Table 1)                 |                |       |            |        |            |          |                |         |                                                     |             |                                                    |

|-----------------------------------------------------|----------------|-------|------------|--------|------------|----------|----------------|---------|-----------------------------------------------------|-------------|----------------------------------------------------|

|                                                     | D7             | D6    | D5         | C/D    | RD         | WR       | Х/Y            | CS      |                                                     | FUNCTI      | ON                                                 |

|                                                     | Х              | x     | х          | Х      | х          | Х        | Х              | 1       | Disable both axes f                                 | or Read/Wri | te                                                 |

|                                                     | X              | x     | X          | 0      | 1          |          | 0              | 0       | Write to XPR byte segment addressed by XBP (Note 3) |             |                                                    |

|                                                     | х              | х     | х          | 0      | 1          |          | 1              | 0       | Write to YPR byte segment addressed by YBP (Note 3) |             |                                                    |

|                                                     | 0              | 0     | 0          | 1      | 1          |          | 0              | 0       | Write to XRLD                                       |             |                                                    |

|                                                     | 0              | 0     | 0          | 1      | 1          |          | 1              | 0       | Write to YRLD                                       |             |                                                    |

|                                                     | 1              | 0     | 0          | 1      | 1          |          | х              | 0       | Write to both XRLD                                  | and YRLD    |                                                    |

|                                                     | 0              | 0     | 1          | 1      | 1          |          | 0              | 0       | Write to XCMR                                       |             |                                                    |

|                                                     | 0              | 0     | 1          | 1      | 1          |          | 1              | 0       | Write to YCMR                                       |             |                                                    |

|                                                     | 1              | 0     | 1          | 1      | 1          |          | х              | 0       | Write to both XCMR                                  | and YCMR    |                                                    |

|                                                     | 0              | 1     | 0          | 1      | 1          |          | 0              | 0       | Write to XIOR                                       |             |                                                    |

|                                                     | 0              | 1     | 0          | 1      | 1          |          | 1              | 0       | Write to YIOR                                       |             |                                                    |

|                                                     | 1              | 1     | 0          | 1      | 1          |          | x              | 0       | Write to both XIOR                                  | and YIOR    |                                                    |

|                                                     | 0              | 1     | 1          | 1      | 1          |          | 0              | 0       | Write to XIDR                                       |             |                                                    |

|                                                     | 0              | 1     | 1          | 1      | 1          |          | 1              | 0       | Write to YIDR                                       |             |                                                    |

|                                                     | 1              | 1     | 1          | 1      | 1          |          | х              | 0       | Write to both XIDR a                                | and YIDR    |                                                    |

|                                                     | х              | х     | х          | 0      | 0          | 1        | 0              | 0       | Read XOL byte seg                                   | gment addre | ssed by XBP (Note 3)                               |

|                                                     | Х              | x     | х          | 0      | 0          | 1        | 1              | 0       | Read YOL byte segment addressed by YBP (Note 3)     |             |                                                    |

|                                                     | х              | x     | х          | 1      | 0          | 1        | 0              | 0       | Read XFLAG                                          |             |                                                    |

|                                                     | х              | х     | х          | 1      | 0          | 1        | 1              | 0       | Read YFLAG                                          |             |                                                    |

|                                                     | X = Don't Care |       |            |        |            |          |                |         |                                                     |             |                                                    |

|                                                     |                |       |            |        | autom      | atically | incremer       | nted at | the trailing edge of I                              | BD or WB p  | ilse                                               |

|                                                     |                |       |            |        |            |          |                | nou u   |                                                     |             |                                                    |

| Absolut                                             |                |       | n Rati     | •      |            | _        |                |         |                                                     |             |                                                    |

|                                                     | mete           |       |            | S      | ymbo       | bl       |                |         | Values                                              |             | Unit                                               |

| Supply \<br>Voltage                                 |                |       |            |        | Vdd<br>Vin |          |                |         | +7.0<br>Vss - 0.3 to Vd                             |             | V<br>V                                             |

| -                                                   | -              | •     |            |        |            |          |                |         |                                                     |             | oC                                                 |

| Operating Temperature                               |                |       | TA<br>Tstg |        |            |          | -25 to +8      |         |                                                     |             |                                                    |

| Storage Temperature TSTG -65 to +150 <sup>O</sup> C |                |       |            |        |            |          |                |         |                                                     |             |                                                    |

| DC Elect                                            | trical         | Chara | acteri     | stics. | (TA =      | -25°C    | C to +80       | °C, V   | 'DD = 3V to 5.5V)                                   |             |                                                    |

|                                                     | meter          |       |            | -      | mbol       |          | Min. Va        |         | Max.Value                                           | Unit        | Remarks                                            |

| Supply V                                            |                |       |            |        | Vdd        |          | 3.0            | )       | 5.5                                                 | V           | -                                                  |

| Supply C                                            |                |       |            |        | Idd<br>Vil |          | -              |         | 800<br>0.15Vdd                                      | μA<br>V     | All clocks off                                     |

| Input Log                                           |                |       |            |        | Vi∟<br>ViH |          | -<br>0.5Vd     | חו      | 0.15VDD<br>-                                        | V<br>V      | -                                                  |

| Output Log                                          |                |       |            |        | VIE        |          | 0.5VL<br>-     |         | -<br>0.5                                            | V           | - IOSNK = 5mA , VDD = 5V                           |

| Output L                                            |                |       |            |        | VOL        |          | -<br>Vdd - 0.5 |         | 0.5                                                 | V           | IOSINK = 5IIIA, VDD = 5V<br>IOSINC = 1mA, VDD = 5V |

| Input Lea                                           |                |       |            |        | lilk       |          | - 00 -         | 0.0     | 30                                                  | nA          |                                                    |

| Data Bus                                            |                |       |            |        | IDLK       |          | -              |         | 60                                                  | nA          | Data bus off                                       |

| Output S                                            |                |       |            |        | IOSRC      | ;        | 1.0            | )       | -                                                   | mA          | VO = VDD - 0.5V, VDD = 5V                          |

| Output S                                            |                |       |            |        | IOSNK      |          | 5.0            |         | -                                                   | mA          | VO = 0.5V, VDD = 5V                                |

|                                                     |                |       |            |        |            |          | 0.0            |         |                                                     | • • • •     |                                                    |

| Transient Characteristics. (TA =                       | -25°C t       | o +80°C)        |           |          |                                                    |

|--------------------------------------------------------|---------------|-----------------|-----------|----------|----------------------------------------------------|

| Parameter S                                            | ymbol         | Min. Value      | Max.Value | Unit     | Remarks                                            |

| For VDD = 3V to 5.5V:                                  |               |                 |           | _        |                                                    |

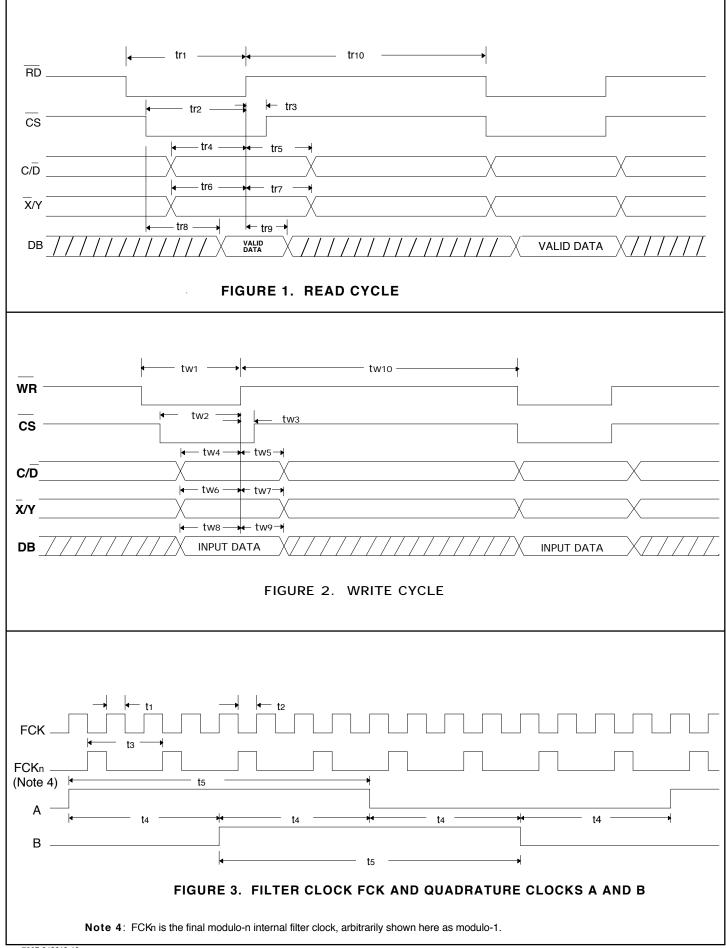

| Read Cycle (See Fig. 1)                                |               |                 |           |          |                                                    |

| RD Pulse Width                                         | tr1           | 80              | -         | ns       | -                                                  |

| CS Set-up Time                                         | tr2           | 80              | -         | ns       | -                                                  |

| CS Hold Time                                           | tr3           | 0               | -         | ns       | -                                                  |

| C/D Set-up Time                                        | tr4           | 80              | -         | ns       | -                                                  |

| C/D Hold Time                                          | tr5           | 10              | -         | ns       | -                                                  |

| X/Y Set-up Time                                        | tr6           | 80              | -         | ns       | -                                                  |

| X/Y Hold Time                                          | tr7           | 10              | -         | ns       | _                                                  |

| Data Bus Access Time                                   | tr8           | 80              | _         | ns       | Access starts when both $\overline{RD}$            |

|                                                        | uo            | 00              |           | 110      | and CS are low.                                    |

| Data Bus Release Time                                  | tr9           | -               | 35        | ns       | Release starts when either RD or CS is terminated. |

| Back to Back Read delay                                | <b>t</b> r10  | 90              | -         | ns       | -                                                  |

|                                                        |               |                 |           |          |                                                    |

| Write Cycle (See Fig. 2)                               |               | 45              |           |          |                                                    |

| WR Pulse Width                                         | tw1           | 45              | -         | ns       | -                                                  |

| CS Set-up Time                                         | tw2           | 45              | -         | ns       | -                                                  |

| CS Hold Time                                           | twз           | 0               | -         | ns       | -                                                  |

| C/D Set-up Time                                        | tw4           | 45              | -         | ns       | -                                                  |

| C/D Hold Time                                          | tw5           | 10              | -         | ns       | -                                                  |

| X/Y Set-up Time                                        | tw6           | 45              | -         | ns       | -                                                  |

| X/Y Hold Time                                          | tw7           | 10              | -         | ns       | -                                                  |

| Data Bus Set-up Time                                   | tw8           | 45              | -         | ns       | -                                                  |

| Data Bus Hold Time                                     | tw9           | 10              | -         | ns       | -                                                  |

| Back to Back Write Delay                               | <b>t</b> W10  | 90              | -         | ns       | -                                                  |

| Load CNTR, Reset CNTR and                              |               |                 |           |          |                                                    |

| Load OL Pulse Width                                    | t11           | 35              | -         | ns       | -                                                  |

| For $V_{DD} = 3V$ :                                    |               |                 |           |          |                                                    |

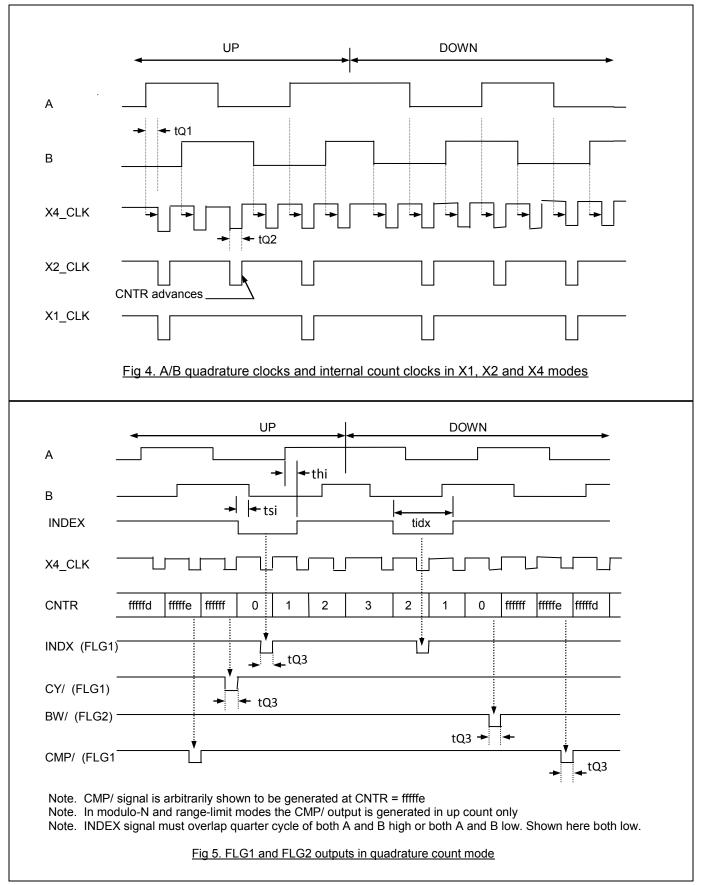

| Quadrature Mode (See Fig. 3-5)                         |               |                 |           |          |                                                    |

| FCK High Pulse Width                                   | t1            | 18              | _         | ns       | _                                                  |

| FCK Low Pulse Width                                    | t2            | 18              | _         | ns       | _                                                  |

| FCK Frequency                                          | €2<br>ffck    | -               | 27        | MHz      | _                                                  |

| Mod-n Filter Clock(FCKn)Period                         | t3            | 36              |           |          | $t_3 = (n+1) (t_1+t_2),$                           |

|                                                        |               |                 | -         | ns       | where $n = PSC = 0$ to FFH                         |

| FCKn frequency                                         | <b>f</b> FCKn | -               | 27        | MHz      | -                                                  |

| Quadrature Separation                                  | t4            | 40              | -         | ns       | t4 > t3                                            |

| Quadrature Clock Pulse Width                           | t5            | 160             | -         | ns       | t5 >4t3                                            |

| Quadrature Clock frequency                             | fqa, fq       |                 | 3.1       | MHz      | $f_{QA} = f_{QB} = 1/(2t5)$                        |

| Quadrature Clock to Count Delay                        | tQ1           | 4t <sub>3</sub> | 5t3       | -        | -                                                  |

| x1/x2/x4 Count Clock Pulse Width                       | tQ2           | 36              | -         | ns       | $t_{Q2} = t_3$                                     |

| Index Input Pulse Width                                | tidx          | 76              | -         | ns       | tidx > 2t3                                         |

| Index setup/hold time                                  | tsi/thi       | 5               | -         | ns       | -                                                  |

| INDX Output Width<br>Carry/Borrow/Compare Output Width | tQ3<br>tQ3    | 18<br>18        | -         | ns<br>ns | tQ3 = (t3 - t2)<br>tQ3 = (t3 - t2)                 |

| Carry Borrow Compare Output Width                      | iQ3           | 10              | -         | 115      | 103 - (13 - 12)                                    |

| Non-Quadrature Mode (See Fig. 6-                       | 7)            |                 |           |          |                                                    |

| Clock A - High Pulse Width                             | t6            | 18              | -         | ns       | -                                                  |

| Clock A - Low Pulse Width                              | t7            | 18              | -         | ns       | -                                                  |

| Direction Input B Set-up Time                          | tbs           | 20              | -         | ns       | -                                                  |

| Direction Input B Hold Time                            | tbh           | 10              | -         | ns       | -                                                  |

| Gate Input (ABG) Set-up Time                           | tgs           | 20              | -         | ns       | -                                                  |

| Gate Input (ABG) Hold Time                             | tgн           | 10              | -         | ns       | -                                                  |

| Clock Frequency                                        | fA            | -               | 27        | MHz      | $fA = (1/(t_6 + t_7))$                             |

| Clock to Carry or Borrow Out Delay                     | t9            | -               | 20        | ns       | -                                                  |

| Carry or Borrow Out Pulse Width                        | <b>t</b> 10   | 18              | -         | ns       | t10 = t7                                           |

| Clock to Compare Out Delay                             | <b>t</b> 12   | -               | 30        | ns       | -                                                  |

|                                                        |               |                 |           |          |                                                    |

| Parameter                         | Symbol        | Min. Value  | Max.Value | Unit | Remarks                                         |

|-----------------------------------|---------------|-------------|-----------|------|-------------------------------------------------|

| For VDD = 5V:                     |               |             |           |      |                                                 |

| Quadrature Mode (See Fig. 3-5     | )             |             |           |      |                                                 |

| FCK High Pulse Width              | t1            | 10          | -         | ns   | -                                               |

| FCK Low Pulse Width               | t2            | 10          | -         | ns   | -                                               |

| FCK Frequency                     | <b>f</b> FCK  | -           | 50        | MHz  | -                                               |

| Mod-n Filter Clock(FCKn)Period    | t3            | 20          | -         | ns   | t3 = (n+1) (t1+t2),<br>where n = PSC = 0 to FFн |

| FCKn frequency                    | <b>f</b> FCKn | -           | 50        | MHz  | -                                               |

| Quadrature Separation             | t4            | 22          | -         | ns   | t4 > t3                                         |

| Quadrature Clock Pulse Width      | t5            | 88          | -         | ns   | t5 > 4t <sub>3</sub>                            |

| Quadrature Clock frequency        | fqa, fqe      | 3 -         | 5.6       | MHz  | $f_{QA} = f_{QB} = 1/(2t5)$                     |

| Quadrature Clock to Count Dela    | y tq1         | <b>4t</b> 3 | 5t3       | -    | -                                               |

| x1/x2/x4 Count Clock Pulse Wid    | th tq2        | 20          | -         | ns   | tq2 = t3                                        |

| Index Input Pulse Width           | tidx          | 42          | -         | ns   | tidx > 2t3                                      |

| Index setup/hold time             | tsi/thi       | 5           | -         | ns   | -                                               |

| INDX output width                 | tQ3           | 10          | -         | ns   | tQ3 = (t3 - t2)                                 |

| Carry/Borrow/Compare Output Width | n tas         | 10          | -         | ns   | $t_{Q3} = (t_3 - t_2)$                          |

| Non-Quadrature Mode (See Fig      | g. 6-7)       |             |           |      |                                                 |

| Clock A - High Pulse Width        | <b>t</b> 6    | 10          | -         | ns   | -                                               |

| Clock A - Low Pulse Width         | t7            | 10          | -         | ns   | -                                               |

| Direction Input B Set-up Time     | tbs           | 12          | -         | ns   | -                                               |

| Direction Input B Hold Time       | tbh           | 5           | -         | ns   | -                                               |